Add a vivado project to synplify pro verification#

Instantiate optimized IP within the HDL code HDL Behavioral Simulation COREGen Functional Simulation Synthesis Implementation Timing Simulation In-Circuit Verification Downloadġ0 Synthesize, Implement, Download Design Verificationīehavioral Simulation Synthesis Implementation Download Functional Simulation Timing Simulation In-Circuit Verification COREGen Synthesize, Implement, and Download the bitstream, similar to the original design flow HDLġ1 Xilinx IP Solutions DSP Functions Math Functions Memory Functions

Add a vivado project to synplify pro generator#

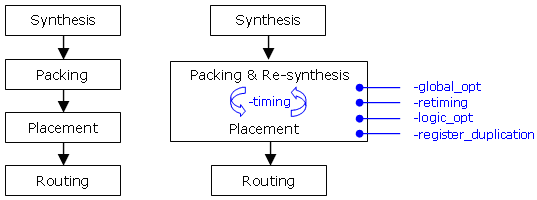

Using the Xilinx System Generator for DSP HDL Co-Simulation Hardware Verification Resource Estimator Summary Simulink Tips and Tricks The designer is responsible for testing and should create the environment for verification.īehavioral Simulation HDL Synthesis Implementation Download Synthesize the design to create an FPGA netlist Functional Simulation Timing Simulation In-Circuit Verificationīehavioral Simulation HDL Synthesis Implementation Download Translate, place and route, and generate a bitstream to download in the FPGA Functional Simulation Timing Simulation In-Circuit Verification If the design does not meet performance, the HDL code may have to be modified.Ĩ Outline Using HDL Using the Xilinx CORE Generator

Synthesis Implementation Download Implement your design using VHDL or Verilog Functional Simulation Timing Simulation In-Circuit Verification Behavioral Simulation In the HDL flow, two sets of codes must be written: HDL design and Verification code (testbench) for Behavioral and Functional simulation. Using the Xilinx System Generator for DSP HDL Co-Simulation Hardware Verification In System Debug Resource Estimator Summary Simulink Tips and Tricks 3 Objectives After completing this module, you will be able to:ĭescribe the advantages and disadvantages of three different design flows Use HDL, CORE Generator, or System Generator for DSP depending on design requirements and familiarity with the tools Explain why there is a need for an integrated flow from system design to implementation Describe the System Generator and the tools it interfaces with Build a model, simulate it, generate VHDL, and go through the design flow Describe how Hardware in the Loop verification is beneficial in complex system designĤ Outline Using HDL Using the Xilinx CORE Generator

0 kommentar(er)

0 kommentar(er)